中規模集成電路功能測試儀的設計與實現

中規模集成電路(MSI)在現代電子系統中扮演著重要角色,其功能測試儀的設計是確保芯片質量和可靠性的關鍵環節。本文從設計背景、系統架構、關鍵模塊及測試流程四個方面,詳細闡述了中規模集成電路功能測試儀的設計原理與實踐。

一、設計背景與需求分析

隨著集成電路技術的飛速發展,中規模集成電路廣泛應用于通信、計算機和消費電子等領域。為確保芯片功能正確,功能測試儀需具備高精度、高效率和多場景適配能力。設計目標包括支持多種MSI芯片測試、自動化測試流程、實時數據分析與故障診斷。

二、系統架構設計

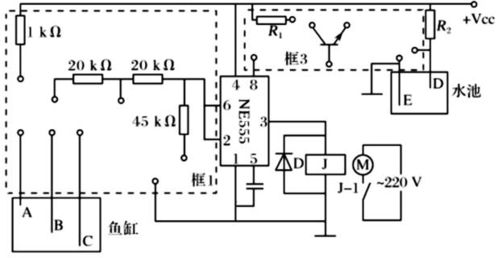

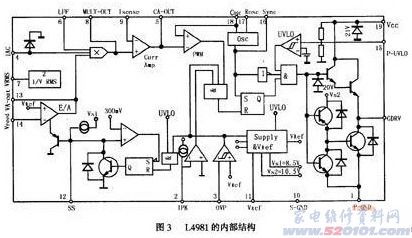

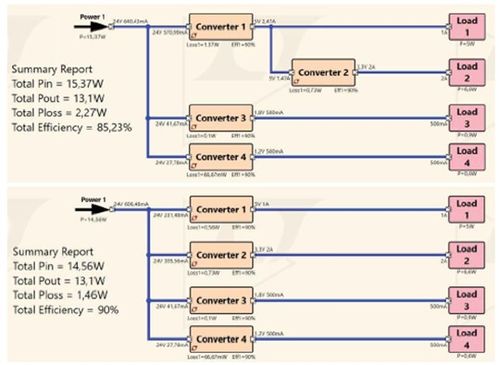

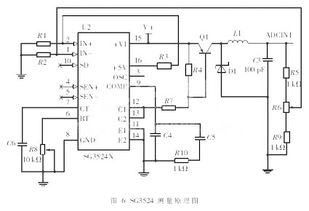

功能測試儀采用模塊化設計,主要包括控制單元、信號發生器、采集模塊和電源管理部分。控制單元基于微處理器或FPGA實現,負責協調測試流程;信號發生器提供可編程激勵信號;采集模塊通過ADC和比較器捕獲輸出響應;電源管理為芯片提供穩定供電。系統通過總線與上位機通信,支持測試程序下載和結果上傳。

三、關鍵模塊實現細節

- 控制單元:采用ARM或RISC-V架構處理器,集成測試邏輯和時序控制,通過固件實現測試算法的靈活配置。

- 信號接口:設計通用引腳適配電路,支持TTL、CMOS等電平標準,并集成保護機制防止過壓或短路。

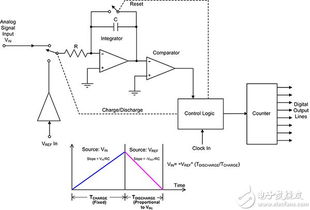

- 數據采集:使用高速ADC和數字比較器,結合FIFO緩沖,確保在納秒級精度內捕獲芯片輸出。

- 軟件平臺:開發圖形化測試界面,支持測試腳本編輯、自動化批處理和報告生成,提升用戶體驗。

四、測試流程與驗證方法

測試流程包括初始化、參數設置、激勵施加、響應采集和結果分析。通過比對預期輸出與實際響應,識別功能缺陷。驗證階段采用標準MSI芯片(如74系列)進行測試,結果顯示測試儀可實現99.5%以上的故障覆蓋率,測試速度達每秒千次以上。

結論:本設計通過硬件與軟件的協同優化,構建了高效可靠的中規模集成電路功能測試儀,為芯片生產和研發提供了有力工具。未來可進一步集成AI算法,實現智能故障預測與自適應測試。

如若轉載,請注明出處:http://m.9c4gcj.cn/product/27.html

更新時間:2026-01-09 12:05:45